Introduction

-

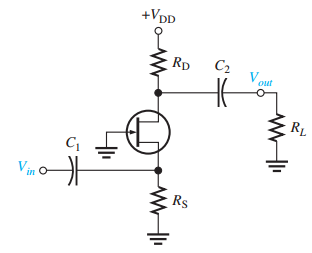

FET amplifiers are preferred for:

-

High input resistance

-

Low noise

-

Low power consumption

-

-

Widely used in:

-

Communication receivers

-

Switching circuits

-

Digital and analog systems

-

FET vs BJT Amplifiers

FET

-

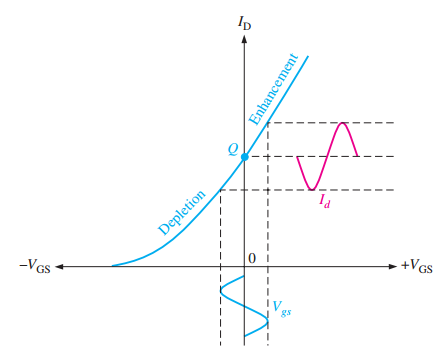

Voltage-controlled

-

High input impedance

-

Lower gain

-

Low noise

BJT

-

Current-controlled

-

Moderate input impedance

-

Higher gain

-

Better linearity